- About company

-

Product

- Inertial Measurement Unit, AHRS, GPS/INS, RTK

- High Performance MEMS Inertial Sensors, Systems and Integrated GPS

- Indoor Location System

- GNSS Simulator, GNSS Test & Software Receiver

- RF Amplifiers

- Cable Laying Equipments

- Quantum Control Stack, DC Source for Quantum Computing Applications

- Precise Time & Frequency for Metrology

- GPS Synchronization Equipments

- Hydrogen Masers

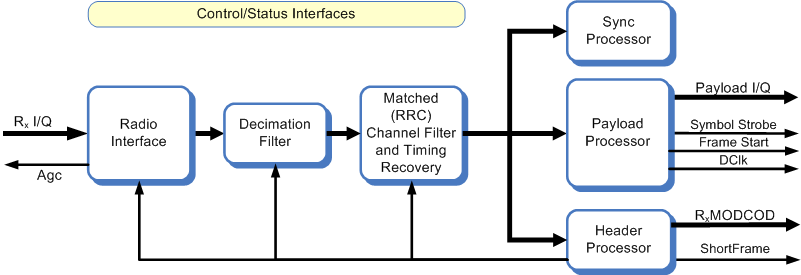

- IP Core Products

- Filter Connector

- Telemetry Systems and Products

- Wireless Data Transmission System

- Partners

- Contact us

- Request for Quote

- Guide

- Products